Plus Too Mac Replica

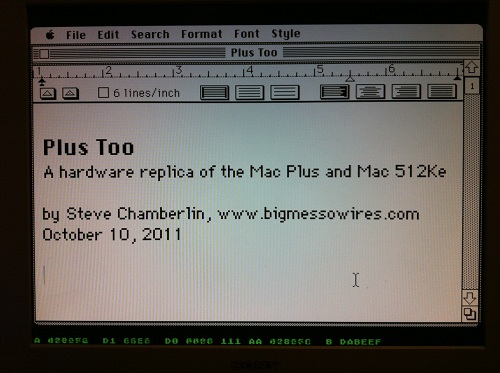

Plus Too is a working hardware replica of the Macintosh Plus and Macintosh 512Ke computers. The project’s goal is to recreate these classic computers using modern electronic components, producing a stand-alone machine able to run period Macintosh software from the mid-1980’s. It is similar in concept to the Minimig Amiga recreation and the Replica 1 recreation of the Apple I.

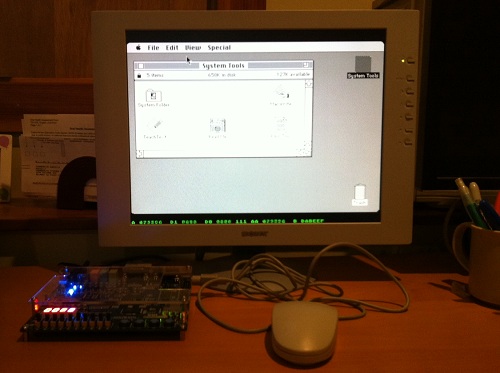

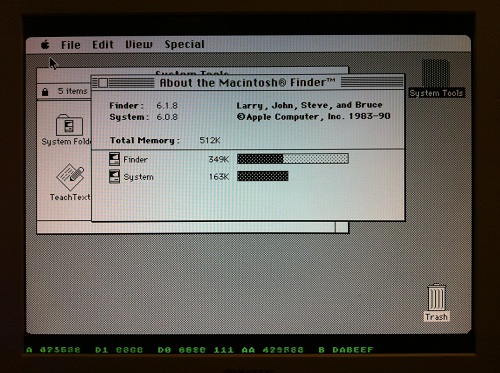

Video output is 1024 x 768 VGA. The Mac’s 512 x 342 screen is pixel doubled to fit the VGA width, which leaves some extra space below the Mac screen region to display hardware debugging information. A standard PS/2 mouse and keyboard are used for I/O. Floppy disk images are planned to be loaded from an SD card, and the current implementation stores a single disk image in ROM. The CPU runs at 8.125 MHz, slightly faster than a real Mac. The current implementation has 512K of RAM.

The original Macs contained a Motorolla 68000 CPU and about half a dozen major support chips, with all of the Mac-specific behaviors and OS routines defined in a 128K toolbox ROM. Plus Too uses an FPGA to model the Mac’s IWM (floppy controller), SCC (serial ports), VIA (general purpose I/O), mouse, and keyboard hardware. The toolbox ROM data was copied from my real Mac Plus (nicknamed “Lonely”) for use with Plus Too.

To correctly model a Macintosh floppy disk, the disk image must be encoded into a series of virtual tracks and sectors, with the proper low-level layout, header, footer, checksum, and GCR disk byte format. This encoding is planned to be performed on the fly by a microcontroller. The current implementation performs the encoding offline, using a custom-made utility program, and the encoded result is stored in ROM.

Status

The current implementation of Plus Too is built using a commercial Altera DE1 FPGA development board. The 68000 CPU is a soft-CPU module within the FPGA. This implementation is capable of booting from a single System 6.0.8 floppy disk image stored in ROM, and running programs from the disk. It exhibits some stability problems, and implements only the absolute minimum of hardware necessary to boot the computer. The disk is read-only, and there is no keyboard, sound, SCSI, serial ports, or real-time clock.

The next version of Plus Too will use a custom-designed circuit board instead of the Altera DE1 kit. The revised Plus Too will use a real 68000 CPU, and will add a microcontroller for the floppy disk SD card interface. It will also add the physical connectors necessary to use a real Mac Plus mouse and keyboard if desired, while eliminating all the extra parts from the DE1 board that are unnecessary for Plus Too. RAM will be increased to 4 MB. The goal is to design a board that is as simple and inexpensive as possible, so that other people can build their own if they wish.

Thanks

Plus Too draws on previous work by many other people. The FPGA models for the Mac Plus mouse and SCC are from an earlier Mac-in-an-FPGA project by Ben Herrenschmidt. Gaining a detailed understanding of the Mac hardware internals was greatly aided by examining the source code for the MESS Mac Plus emulator and Mini vMac emulator. The FDisasm tool was used to generate a commented disassemply of the toolbox ROM routines, which was a tremendous help.

More Details

Download the Plus Too file archive, and learn how to set up your own Plus Too.

View the detailed build log for Plus Too.

24 comments

24 Comments so far

Leave a reply. For customer support issues, please use the Customer Support link instead of writing comments.

[…] describes his success over at his blog: Plus Too is a home-made replica of a classic Macintosh computer using an FPGA. The project reached a major […]

[…] out the Plus Too over on the ‘Big Mess o’ Wires‘ site – it’s a hardware replica of a […]

Based on what you have done thus far, do you think it would be feasible to create something similar to recreate the Apple IIGS? I have aspirations to create something like this, and I know that the Altera board you use would have by far more power than would be required for the IIGS. I know that the IIGS CPU has already been virtualized for the FPGA, and I’m hoping that sometime I could use the IWM code to jumpstart my development.

I don’t see any reason why a IIGS replica couldn’t be built in a similar way, although I’ve never personally looked at the Apple II hardware in detail. Yes, the IWM part should be nearly identical between the IIGS and the Mac, I think. You’re welcome to use my code for that if you’d like.

I’d like to discuss this at your convenience as I would definitely like to help out here if possible. My C skills are alright, but they could use some work, and helping set this up would sharpen my skills. I didn’t see a source link on your page. Are you hosting this on google code or something?

Eventually I’ll have it here or Google Code, but it’s not really ready for other contributions yet. The code’s still a big pile of half-finished ideas that only partly work. 🙂

How far do you plan to go as far as feature completeness is concerned? For example, do you intend to implement SCSI, sound and other peripheral interfaces? What about things like the ADB? I’m following this with keen interest with a view to making a classic Mac ‘laptop’

sound – Yes

SCSI – Unsure, it will probably be just a floppy initially, but SCSI is a possibility.

ADB – No, since the Mac Plus and earlier computers didn’t use ADB. I believe I’ve seen a couple of recent ADB emulator projects if you need that, though.

Steve, I was wondering about code only so I could purchase a altera dev board and get it running with the code you have, even if its in binary form.

I understand about not yet letting code out there, but I just wanted to use something like this in its functional form, then take a look at the guts of the code to see how things work. This would definitely be getting waist-deep in altera soft-core programming, even if It’s just download code, compile and upload kinda thing.

Even this much functionality is amazing, and I’d love to get this setup for myself.

I’m pretty sure that holding down the mouse button on startup is supposed to eject the disk. There was no exposed eject button on any Mac, ever. You could however use a straightened paper clip in an emergency.

I have been wanting to do this project for a while now. I have a lot of information that might be helpful. My plans were to implement a custom component that would replace the floppy controller with an sd or usb host. This would bypass all the problems of the disk incompatibilities because it would be working on the bit level. I found schematics of the mac 128k/512k as well as the notes for reverse engineering all the PAL chips. Another good source was the original Byte review of the Mac, it has a surprising amount of technical detail. I also looked at the mac 68k linux project. They have a lot of technical information about the Mac plus that includes interfacing with the hardware. It could be a good place to find out how to replace components with updated versions.

Awesome project, I have a similar project in mind, but with a different concept: I plan to use the original ASICs and construct a multi-apple platform consisting of an Apple IIe, Macintosh Classic, and a beefed up LC575(WIth 40MHz CPU). Even though I will utilize the original ASICs for the most part, this will not simply be a re-layout of the existing designs. I want to utilize high speed muxes to allow for shared resources(But not simultaneous operation of the platdorms). At boot up time you will select which machine you want from a boot picker and also select floppy and hard drive images from removable compact flash cards. There will probably be two slots – one to hold virtual SCSI hard drive images, and one to hold virtual floppy images with a catalog of volume names. The drive emu will be quick and dirty, so there will likely be wasted space as 1.44MB floppy images will start on even 2M boundarys and such. Some of the extra space will hold meta data for the boot picker catalog etc. The whole thing will go into a modern+retro inspired milled aluminum and glass enclosure with a modest sized LCD (10×7 13″-15″) Some custom silicon will be required(read FPGAs), but using the existing ASICs will speed up development time as it would take years to reverse engineer the existing ASICs and I want the machine to be reliably stable and usable. I’ll be starting a blog when the project starts proper a few months from now.

Haha forgot spell checking – that’s supposed to be platforms above, not “platdorms”.

Only discovered your website a few days ago when a friend alerted me to it! Nice work! I’ve done a few micro implementations, including C64 and TRS-80 using raw disk formats. The former were converted on-the-fly from D64->G64 by an embedded micro, the latter was pre-formatted and stored in flash (like you’re doing).

Your project has given me the impetus to give the Mac a go; I’ve been thinking about doing it for quite some time. It won’t be as accurate as yours, just enough to get something running. For example, I’m using dual-port video ram, so no RAM arbitration required.

Tonight I just managed to get 24KB of video RAM (initialised from a screen dump from MESS ($1A000-$1FFFF)), displaying on VGA (800×600). Can see the mouse pointer and the ‘question’ disk…

Hmmm… I’ve added the TG68 core, 64KB ROM and 32KB RAM. Added a quick hack for cold-start vectors, and I can see it’s executing the ROM as expected. Added VBLANK, 1Hz signals and wired to the 6522 PIA (taken from the FPGA64 project IIRC). Same hacks as you for IWM and auto-vectors (I no idea how the latter are supposed to work, BTW).

No changes on the video. No interrupts generated by the PIA.

About to start tracing the execution. Any caveats with only 32KB RAM? It’s aliased over the whole 128KB space – could that cause problems?

I’ve been thinking about adding debug capability to a few soft cores for a while now. For your TG68 breakpoints, did you simply gate the CPU clock-enable with a comparator on the address bus? Or did you use other (and/or internal?) signals from TG68 to qualify the halt condition? eg. AS?

This is an amazing project! I can’t wait to see where it goes from here!

Dude, this is awesome.

This is even more awesome than the Minimig.

I want one.

I can’t wait until this is finished. It would be so fun to use. XD

I hope you put in a built in monitor. It would be cool to make it look a little bit like the original Mac 512k.

Too bad you can’t buy some cheap mice and keyboards and mod them to be wireless replicas of the original ones xD.

About SCSI, I have that going in minimigmac, feel free to borrow it since you already have the mouse & kbd 🙂 It uses the PIC of the minimig board to emulate the SCSI commands and does some HW handshaking to ensure no bytes are lost even in “Blind” mode since I cannot quite reproduce good enough timings from the uC talking to the SD-CARD to make the old Mac+ drivers happy. In the end that makes it more reliable than the real Mac+ SCSI.

The main problem of course is that the Mac ROM loads the SCSI disk driver from the SCSI disk itself, and the Apple Installer (at least the orignal ones) only recognizes a handful of specific disks so you have to either mimmic one of these or hack the driver on the disk.

I started at some point writing a replacement / free SCSI disk driver (I used to know how to do that about 20 yrs ago) in m68k asm but eventually decided I had better uses of my time 🙂

Hi, I own a DE1, could you please share the binaries of this awesome project?

The binaries are in the Plus Too file archive, linked above.

Hey big dog.

I feel like you beat all the Bushes, You have this…. You have Katy, You have Tiny CPU.

Why no go right for the gusto?

Something that has a little bit of floppy/HD20 emu, Katy/Tiny CUPU/PLus Two/Plus R/W Romage.

Maybe you will connected the dots you cool dude?

Update: http://www.bigmessowires.com/2015/10/22/plus-too-mac-replica-new-progress/

Based on what you have done thus far, do you think it would be feasible to create something similar to recreate the Apple IIGS? I have aspirations to create something like this, and I know that the Altera board you use would have by far more power than would be required for the IIGS. I know that the IIGS CPU has already been virtualized for the FPGA, and I’m hoping that sometime I could use the IWM code to jumpstart my development.