Tetris Max Worldwide High Score Contest is Saturday

Here’s your reminder for the first ever Tetris Max Worldwide High Score Contest, happening this Saturday October 14 from 11:00 am to 3:30 pm Pacific Daylight Time (UTC−07:00). Warm up your wrists, live stream your efforts, and enjoy that great music from Peter Wagner. The top scorer wins a $100 gift certificate to the BMOW Store. Will there be other prizes too? Does a level-up sound say moo? See the complete contest rules for details. Good luck to everyone!

Be the first to comment!Mac-to-VGA Sync-Splitter Prototype

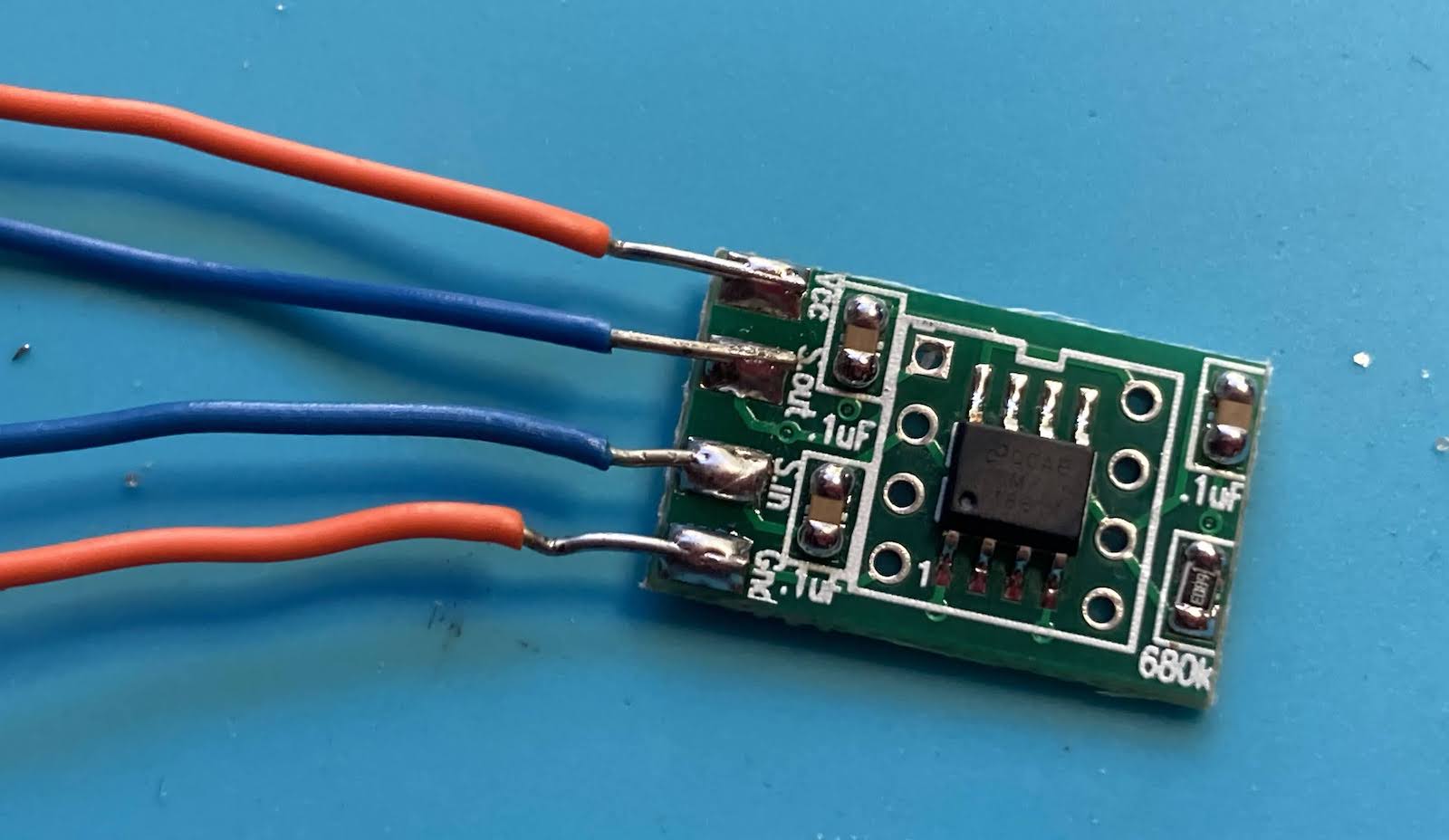

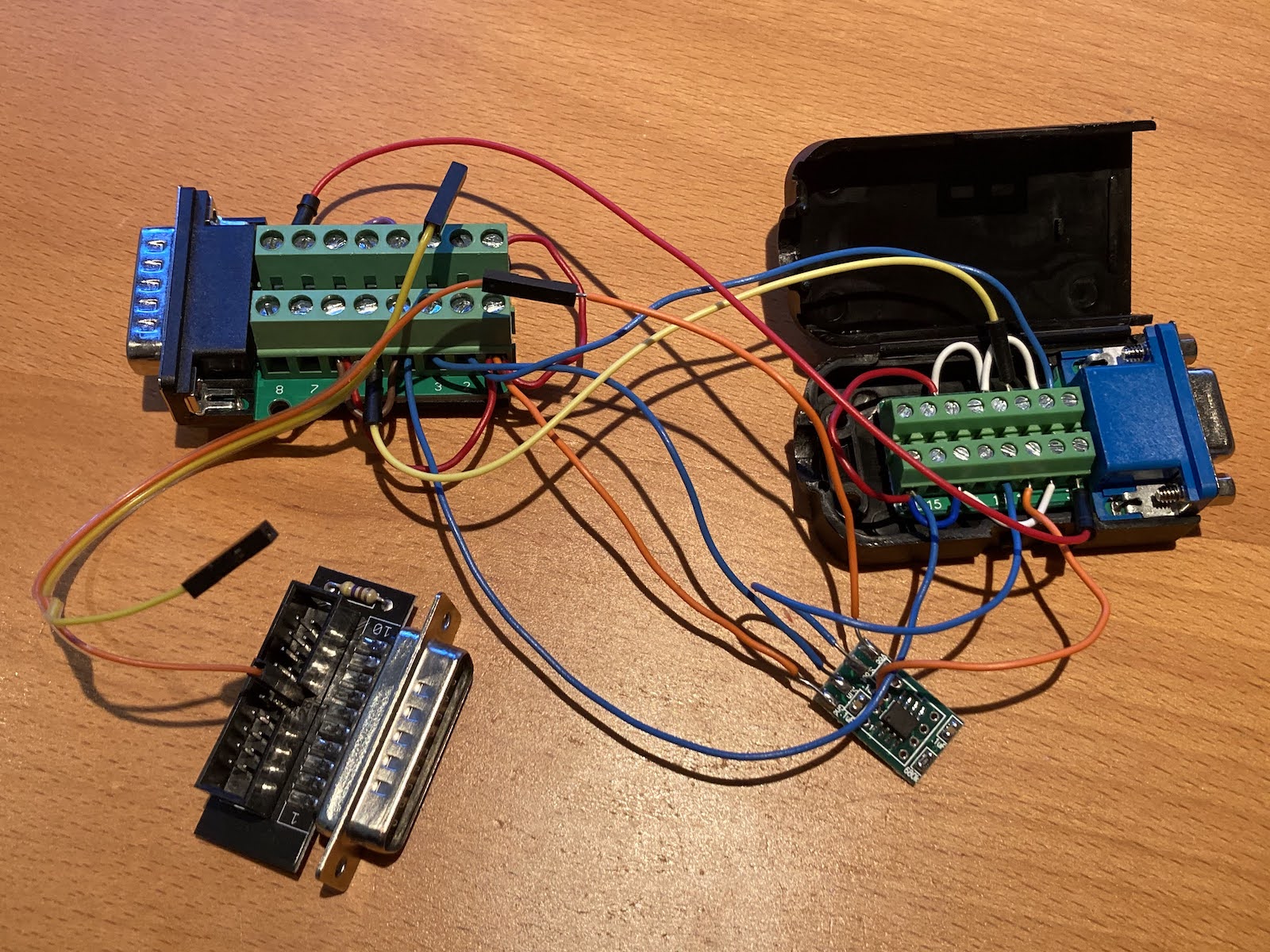

Elapsed time: 122 hours from design concept to finished product in my hands. Hey, it works!

Last week I wrote about my attempts to design a Macintosh-to-VGA video adapter with an integrated sync splitter, separating composite sync into the separate hsync and vsync signals expected by most VGA monitors. I bodged together a proof-of-concept circuit using an LM1881 chip, which sort-of worked on some of the monitors I tested. After that, my goals for this prototype PCB were:

sync detection LEDs: Two LEDs to visually indicate whether the Mac is putting out composite sync, separate sync, both, or neither.

self-powering: The chips in the adapter should be powered by rectifying the sync signals themselves, instead of requiring a separate 5V supply.

usable VSYNC: The extracted vsync signal from the LM1881, when combined with the original csync, should enable at least some monitors to work with my Mac that didn’t work before.

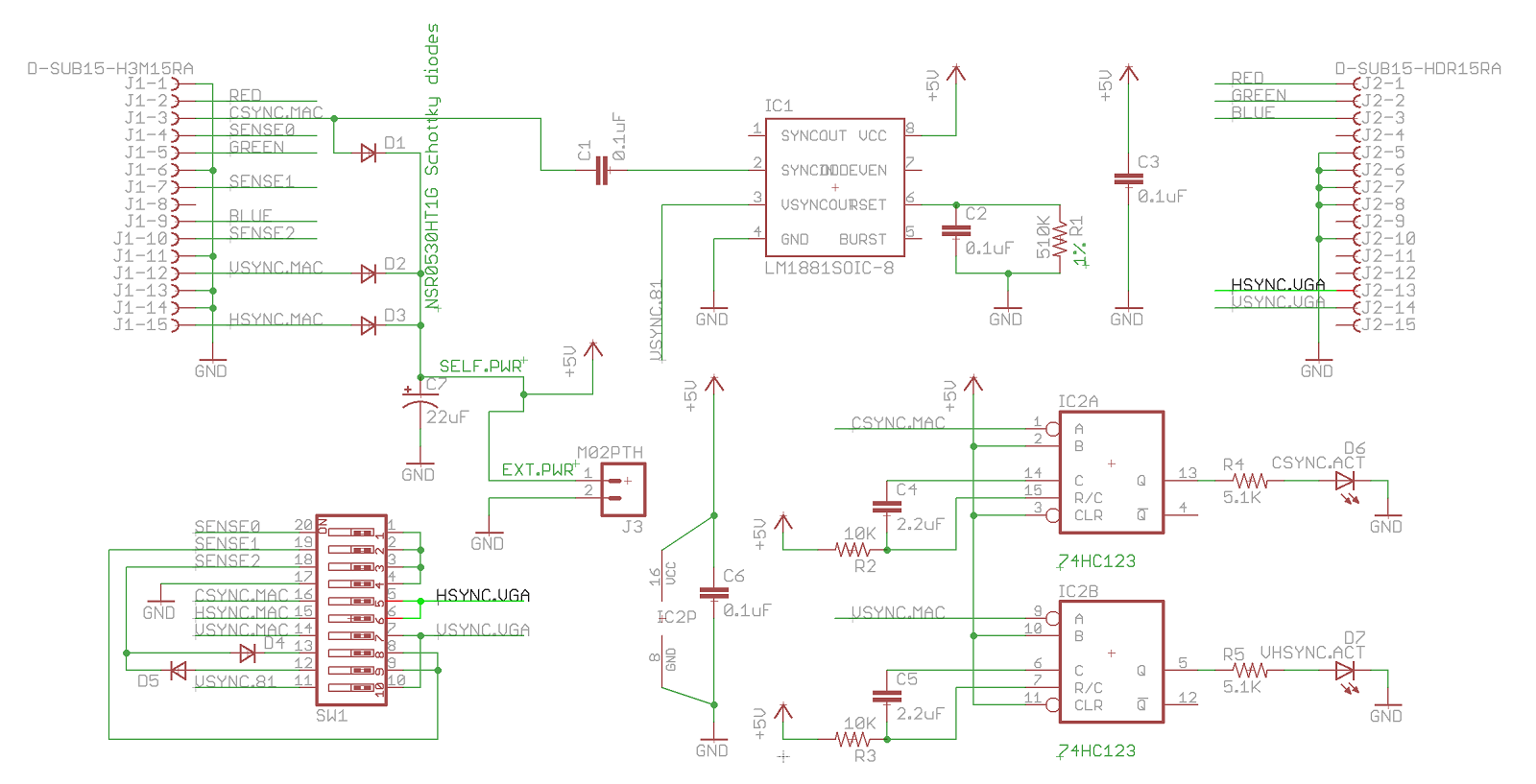

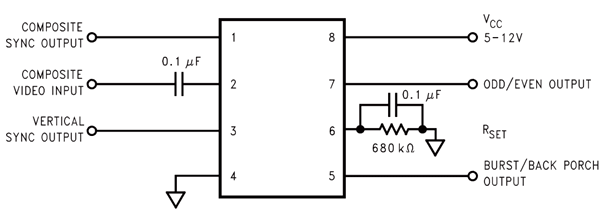

Here’s the PCB schematic:

There are two specific elements worth mentioning here. One is the LM1881 RSET resistor, which is 680K ohm in the LM1881 reference design, but I lowered it to 510K ohm here in a belief that this value would be more appropriate for Mac video resolutions.

The second element is the way the Mac’s csync signal is applied directly to the LM1881 video input at pin 2 (or “directly” through a blocking capacitor), instead of first passing through a resistor voltage divider to reduce csync to the approximate voltage level of a composite video signal. I experimented with both approaches, and an earlier schematic used the divider. But I think the combination of the resistor divider and the blocking capacitor formed an unwanted RC filter, resulting in oscillation and strange behavior. I could have taken further steps to address this, but since many other people have used 5V sync inputs with the LM1881, and it appeared to detect the sync just fine, I used the simpler approach without the divider.

Shiny New Prototype

My first prototype was an ugly mess of wires and breakout modules, and it didn’t even try to implement sync detection LEDs or self-powering, so I was excited to try this new prototype PCB. I’m happy to report that sync detection works, for both csync and h+vsync. In an effort to reduce the adapter’s current consumption, the LEDs are powered with less than 1 mA of current, but are still easily visible. This is exciting and this feature alone is a great diagnostic tool. At this weekend’s Mactoberfest Meetup, you can bet I’ll be running around plugging one of these adapters into every Mac and Nubus video card that I can find, and making a list of which ones output csync, separate H+V sync, or both.

The self-powering also works. The self-powered supply voltage (diode rectified from the sync signals) results in a VCC about 4.09V. That seems to be high enough for the chips to work, but we’re in uncharted territory for the LM1881 and it may not work completely correctly at this voltage. The Schottky diodes used for rectifying should drop about 0.3V from 5V, so why isn’t VCC 4.7V? Well, there’s also a 180 ohm series resistor on each of the Mac’s sync outputs that will cause additional voltage drop, and the sync output drivers also have some internal resistance. Based on these numbers, I estimate the adapter is drawing about 3.3 mA (0.6V drop divided by 180 ohms) from each of the three sync signal outputs, or about 10 mA total.

It’s great that self-powering works, but the resulting VCC is lower than I would have hoped, and the dependency on that 180 ohm series resistor is troubling. If other Macintosh models and video cards have a larger series resistor or a higher internal resistance on their sync output, then self-powering might not work.

The vsync signal that’s output from the LM1881 has a voltage during its high parts of only about 2.65V. I think 2.65V is still high enough to be a valid logical high voltage when seen at the monitor, but it’s cutting it close. I might add a buffer or transistor here to bring the vsync signal all the way up to VCC, if it doesn’t increase the adapter’s current needs much.

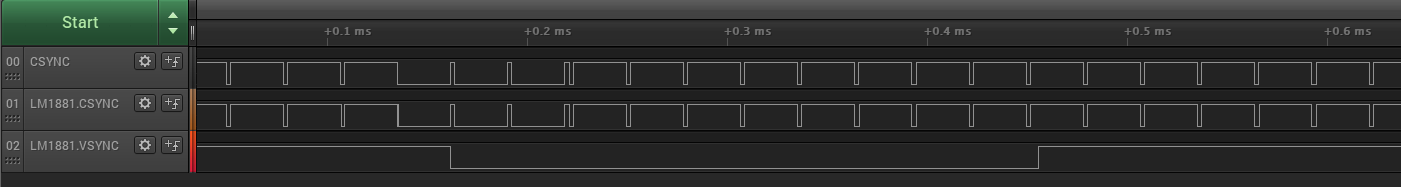

There’s a second oddity about the LM1881’s vsync output with this prototype, aside from the voltage: the vsync pulse width is significantly longer than with the first protoype (about 16 lines versus 10), and it’s also variable (from about 15-17 lines on any given frame). The falling edge of the vsync pulse always comes at exactly the same spot relative to csync, but the time until the rising edge is variable. With my change of RSET from 680K ohm to 510K, the vsync pulse width in this new prototype should have been shorter than before, not longer. I’m not sure if this odd behavior is because of the lower VCC, or because one of my other component values is wrong, or what.

I can try all this again using a 5V external supply, instead of self-powering, and see how things change.

Field Testing

So does it actually work for separating hsync and vsync? The answer is yes, sort of. On my Dell 2001FP monitor it works, but the picture jumps up and down vertically by a couple of lines, probably due to the problems with VSYNC. I wouldn’t have guessed that the timing of vsync’s rising edge mattered much, so this is a little surprising.

I just received a Dell EL151FP monitor, which doesn’t work with the IIci normally, but does work via this adapter. Awesome! However once again there’s some vertical jitter.

My Viewsonic VG900b doesn’t work. This is the pickiest monitor in my stable, and it didn’t work with my first prototype either.

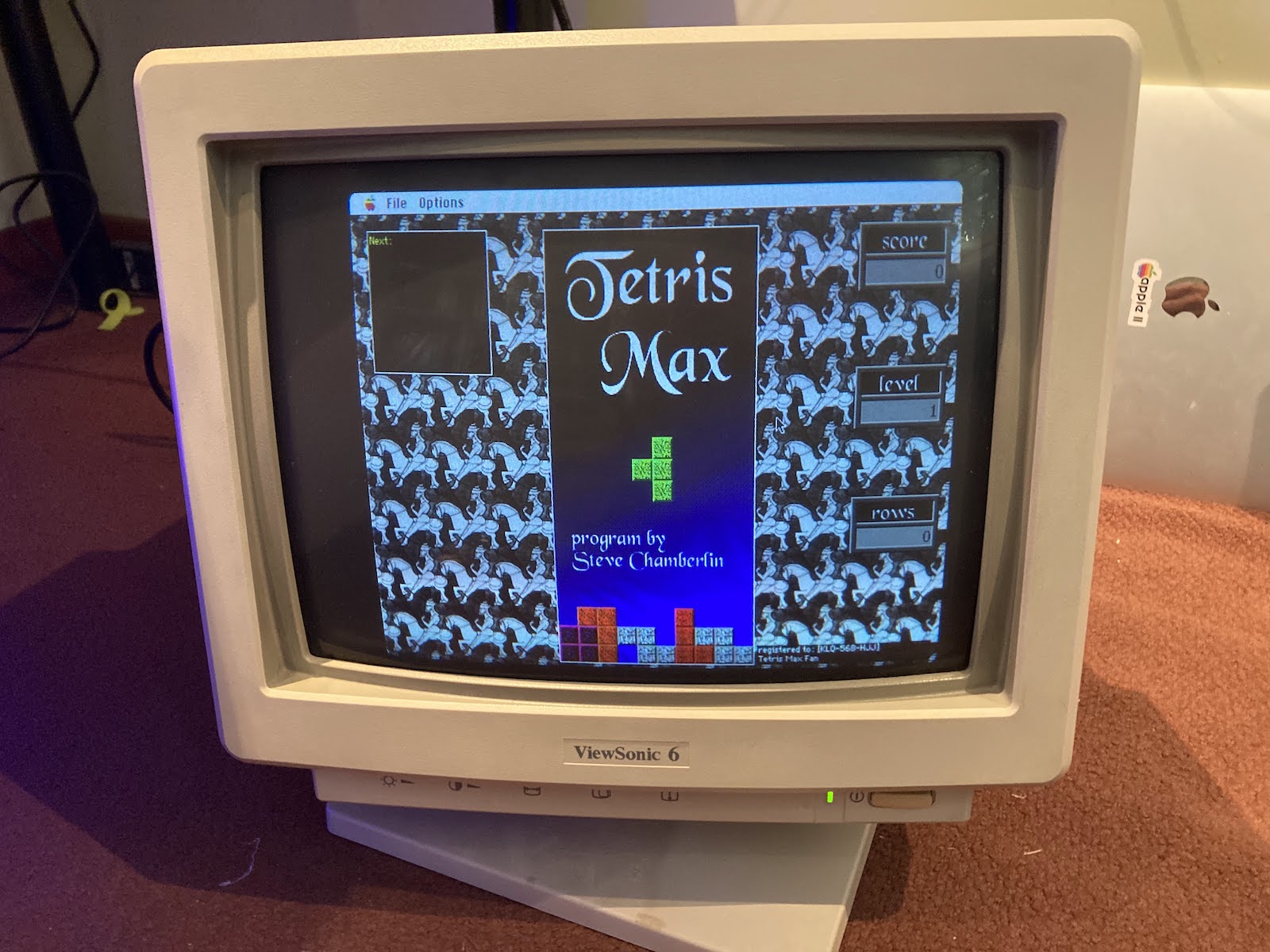

The Viewsonic 6 CRT works. This monitor doesn’t work with the Mac IIci normally, so this proves the adapter is doing something useful.

Goodbye LM1881, Hello MCU

As promising as this second prototype is, I’m not going to pursue this LM1881 design further. I’m not going to switch to a different sync-splitting chip either. It finally dawned on me that all the sync splitting chips are designed to do something much more complicated than I need: they’re meant to extract sync signals from a composite video signal that contains actual video data, chroma bursts, and negative-going sync, all at low voltage levels around 0.7V. But I don’t need any of that – I already have a 5V composite sync signal and I merely need to extract HSYNC and VSYNC from it.

After giving it some thought, I decided that the best path forward is to use a microcontroller to process the input sync signals, extract HSYNC and VSYNC, turn on the activity LEDs, and do anything else that’s needed. This will create some new challenges like clock-based jitter and VCC-imposed limits on clock speed, but it will turn this into more of a firmware plus circuit design problem, instead of a “read the datasheet” problem involving some complicated sync chip designed for a different purpose than mine.

I’ve already had some success with testing this approach, and in fact I was able to get a usable video image from the Mac IIci on the Viewsonic VG900b monitor, which had rejected all my prior attempts at feeding it synthetic sync signals. There are still more problems to work out, though. More updates coming soon.

Read 7 comments and join the conversationYellowstone Disk Controller Begins Second Production Run

I’m happy to report that BMOW’s Yellowstone Universal Disk Controller for Apple II computers is beginning its second production run. I’d long thought that Yellowstone would be a once-and-done project, because a key chip used in its design became unobtainable anywhere late during the development phase. I was only able to make an initial production run because I’d had the foresight to stockpile parts six months earlier. The global semiconductor shortage was wreaking havoc, and for more than two years these parts remained unavailable at any price from the chip manufacturer or distributors. But in the past few months the chips have finally become available again, and while they’re not priced cheaply, at least they’re obtainable.

Yellowstone is a universal disk controller card for Apple II computers. It supports nearly every type of Apple disk drive ever made, including standard 3.5 inch drives, 5.25 inch drives, smart drives like the Unidisk 3.5 and the BMOW Floppy Emu’s smartport hard disk, and even Macintosh 3.5 inch drives. Yellowstone combines the power of an Apple 3.5 Disk Controller Card, a standard 5.25 inch (Disk II) controller card, the Apple Liron controller, and more, all in a single card.

Be the first to comment!Electric Bow Tie 3000 Reloaded

Ah, the Electric Bow Tie 3000: BMOW’s least-loved product. The bow tie was retired several years ago, but it’s still possible to make your own annoying neckwear device! I’ve belatedly uploaded the schematic, PCB files, parts list, and instructions here. For those who’ll be attending Mactoberfest Meetup this weekend, I’ll be giving away some Electric Bow Tie kits. These include the PCB, LEDs, and CdS photocell. The other parts (buzzer, 555 timer, etc) are available from DigiKey, Mouser, and other electronics suppliers.

Be the first to comment!Mactoberfest Meetup is One Week Away!

The Mactoberfest Meetup classic Macintosh celebration is only one week away!

What is this?

Mactoberfest Meetup is a free social event for classic Macintosh computer collectors in the San Francisco area, and their Apple II friends. Attendees are bringing their computer collections to display, and we’ll also have a flea market, a freebies table, a workshop area, and a Tetris Max high score competition. It’ll be a fun day poking at old computer hardware and revisiting the days of Hypercard, desk accessories, and flying toasters! We’re expecting about 40 collection displays and 100 people total.

Where and when is the meetup?

Saturday October 14, 11:00am to 5:00pm, in Belmont California. RSVP here for the address.

Where can I park?

There’s parking for 65 cars in the lot at the venue. Overflow street parking is available nearby. Attendees who aren’t bringing any equipment are asked to park on the street, and leave the parking lot spaces for people with heavy computers to unload.

What equipment should I bring?

One or more pieces of classic 1980s and 1990s Macintosh gear, or Lisa / Apple II computers, Newtons, eMate, QuickTake cameras, Macintosh clones, printers, routers, software media, documentation, books, souvenirs…

How should I prepare my equipment?

Bring your own extension cords and power strips. Label everything with your name. Plan defensively for equipment safety: you are assuming the risk of accidental spills, damage, loss, etc.

What software should I run on the computer?

Please avoid having computers idling at the Finder desktop. Load the computer with your favorite classic game, content creation software, screen savers, demos, or anything else that others might enjoy experimenting with.

How will the equipment be displayed?

We’ll have several rooms furnished with chairs and 72 x 30 inch banquet tables. Everyone will have at least half a table to display their equipment, with extra space available for people with larger collections.

How will the flea market work?

We expect to have several dozen people bringing classic computer gear to sell. For-sale items may be located at the display tables or in the designated for-sale area of the building. Please tag your for-sale items with your price and your name / phone number, so interested buyers can text/call you if you’re not standing next to the items all day. You can use this template for sales tags.

What’s the Freebies Table?

It’s a dedicated area for donating extra items you no longer need, for other people to take. Disk drives, mice, keyboards, cables, floppy disks, peripheral cards, books, whole computers… If you see something you want here, take it!

What’s the Workshop Station?

It’s an area stocked with tools for troubleshooting and repairing computers, or building project kits. Expect to find soldering irons, tools, a multimeter, and maybe an oscilloscope or logic analyzer.

What are the project kits?

BMOW is donating ATX to Macintosh 10-pin power supply adapter kits that can be assembled with easy soldering. Donations of other DIY kits and electronic or mechanical projects are appreciated.

What’s the plan for LAN games?

Bring your LocalTalk PhoneNet cables if you have them. We’ll organize teams for network play of Bolo and other classic Mac network games.

How will the Tetris Max high score competition work?

At least two dedicated Tetris Max stations will be running all day. The best score achieved by the afternoon deadline will win a complete Macintosh Performa 460 computer system. You must be present at the time of the contest’s end to win. See the complete rules for details.

What else can I bring besides classic computer gear?

Please bring your tools and parts for the Workshop Station: multimeters and test equipment, irons, grips, mats, screwdrivers, tweezers, pliers, cutters, spare parts, etc.

Will food be provided?

No, there won’t be food vendors or catering at the meetup location. There’s a shopping mall nearby with a grocery store and restaurants.

Really, no food?

Please consider bringing snacks or drinks to share; this is a free event and we all participate in making it a success. Good options might be fruit/vegetables, granola bars, mini sandwiches, crackers and chips, and canned or bottled drinks. Avoid open beverage containers or foods that are messy and have higher risk of spills into keyboards. The venue has utensils and plates if needed. Any plasticware must be compostable or recyclable, no disposable plastic is permitted.

How else can I help?

If you have time, stick around after the meetup to help tidy up and put things away. Thank you!

How can I share Mactoberfest photos?

Please take lots of photos! Send them to mactoberfest@bigmessowires.com and we’ll create a post-meetup album so everybody else can see what they missed.

E-WASTE NOTE: Everything you bring to Mactoberfest must be taken home with you at the end of the day, unless it’s sold or positively claimed at the Freebies table. Don’t abandon any equipment or parts at the meetup site. Don’t put e-waste into the building’s trash cans or dumpster. Thanks for your understanding.

Let me know if you have any other questions. I’m looking forward to seeing you all soon!

Classic Macintosh Video Signals Demystified, Designing a Mac-to-VGA Adapter with LM1881

In the late 1980s When Apple released its first Macintosh models supporting external color monitors, the company made some design choices that continue to cause trouble even today. Computers like the Macintosh IIci supported 640 x 480 video resolution, the same resolution as the VGA standard that was common in the PC world, but they used a different physical connector for the monitor cable, a different vertical refresh rate, and a different method of encoding sync information. It’s those sync differences that have proven to be most problematic over the years. Let’s look at what all is required to use my Macintosh IIci with a modern LCD monitor. Grab some coffee and get comfortable, because this will be a long one.

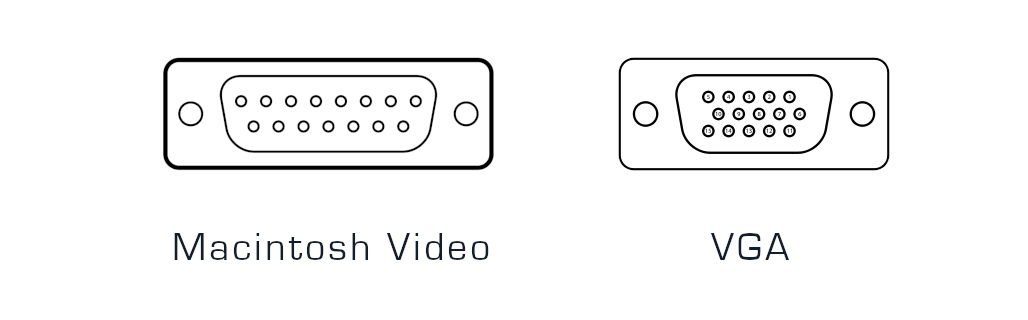

Monitor Connector Comparison

The classic Macintosh video connector is a DB-15, with two rows of pins. The correct name for this is actually DA-15, but nearly everybody calls it DB-15 and we’ll follow that convention. The VGA connector is a DE-15 with three rows of pins. This is sometimes called HD-15 owing to its “high density” arrangement of pins. Despite the physical differences, the video signals on the two connectors are mostly the same: (pinout data from sfiera)

| Signal | Mac | VGA |

| Red video | 2 | 1 |

| Red ground | 1 | 6 |

| Green video | 5 | 2 |

| Green ground | 6 | 7 |

| Blue video | 9 | 3 |

| Blue ground | 13 | 8 |

| HSYNC | 15 | 13 |

| HSYNC ground | 14 | 5 |

| VSYNC | 12 | 14 |

| CSYNC | 3 | NC |

| VSYNC/CSYNC ground | 11 | 10 |

| Sense 0 | 4 | NC |

| Sense 1 | 7 | NC |

| Sense 2 | 10 | NC |

| Ground | shell | shell |

This difference in physical connectors is fairly easy to solve with an adapter. During the 1990s and 2000s you could find a Mac-to-VGA adapter at any computer store. Today they’re more rare, but still available from surplus electronic suppliers or eBay.

Signals and Sync

A very brief primer on video signal formats: A video signal is composed of a series of lines, organized into frames. The lines are output from the video hardware one by one, at a fixed rate, and the timing of each line is indicated with an HSYNC pulse from the video hardware. After all the lines in a frame have been output, there’s a VSYNC pulse before the start of the next frame. The monitor needs these sync pulses to keep its display operating in lockstep with the video signal.

The 640 x 480 VGA standard uses 60 frames per second – its vertical refresh rate is 60 Hz. But Apple chose a 67 Hz refresh rate for its 640 x 480 video format (actually 66.666666…), which could be argued is slightly better than 60 Hz because the higher rate results in reduced flickering on CRTs. The difference is negligible, however, and the 67 Hz rate only serves to complicate things. Fortunately most modern moderns support a fairly wide range of vertical refresh rates, where a range like 50-75 Hz is common. This means that the 67 Hz refresh rate usually isn’t a problem. If you know of a counter-example, please tell me.

What about those sync signals? In the VGA standard, HSYNC and VSYNC are provided as separate input signals on VGA pins 13 and 14. It’s nice and simple, end of story. But in the classic Macintosh video world, sync is… complicated. There’s a fair amount of misunderstanding and myth about this topic floating around the web, so I’m here to explain the truth. From the table above we can see that the Mac has outputs for HSYNC and VSYNC, but also for CSYNC composite sync (HSYNC xor VSYNC). Many people have also heard about sync on green, where composite sync is mixed directly into the green video channel. So what exactly is the Mac video sync standard? Does it output separate HSYNC and VSYNC, or CSYNC, or sync on green?

The answer is yes, the Mac generates all of those sync standards at different times, depending on what type of monitor it thinks is connected. But it doesn’t generate all of them all of the time. The video hardware checks the voltages on the connector’s three sense pins, which form a 3-bit monitor ID for the connected monitor type. If it’s a supported monitor type, the video hardware configures itself for an appropriate output signal and sync method. If it’s not a supported monitor type, the video hardware shuts off and outputs nothing.

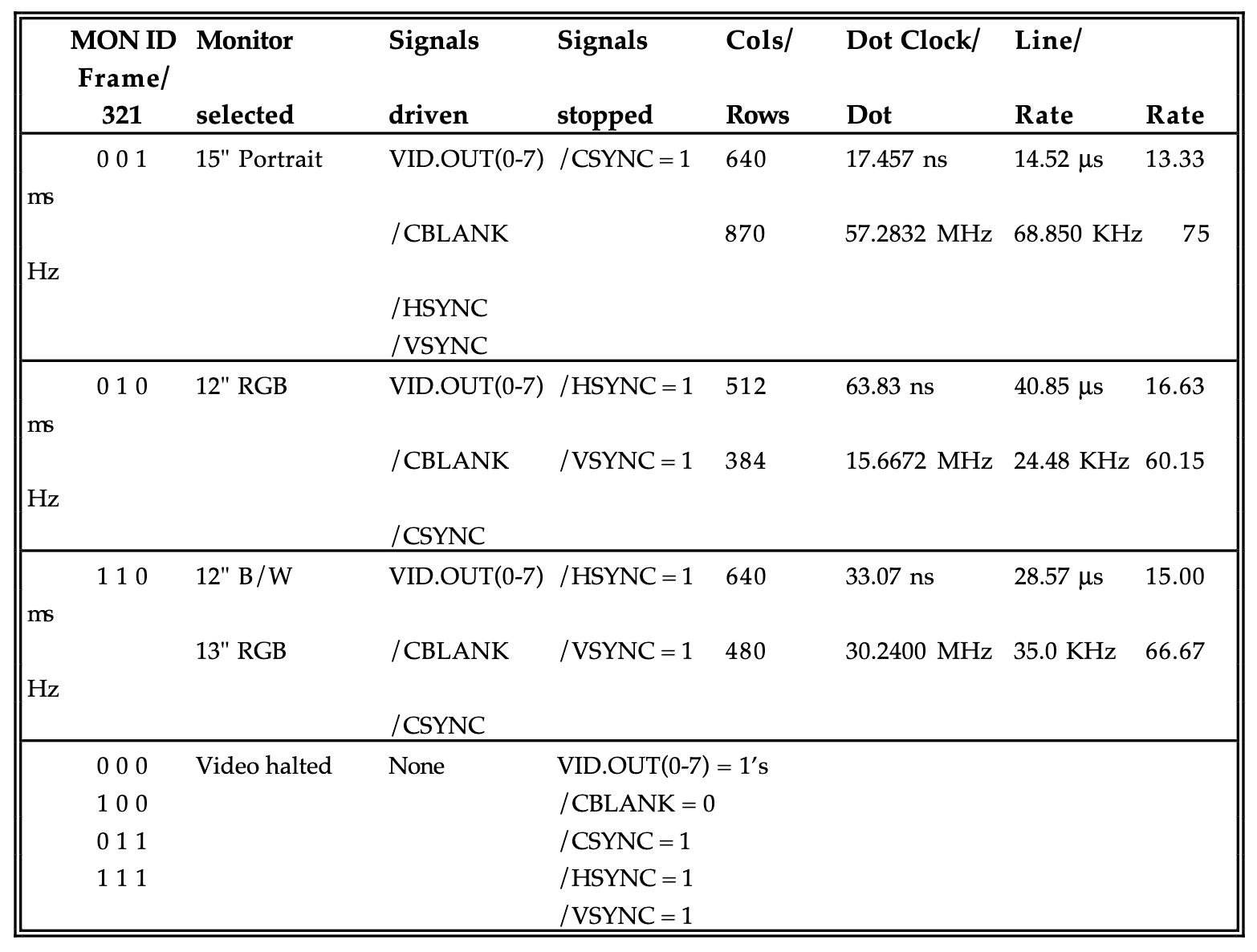

Here’s a page from a Macintosh IIsi hardware developer note. The IIsi’s video hardware is nearly identical to my IIci:

We can see that four different types of monitors are supported, but two of them share the same monitor ID and signal format. For a 15 inch portrait monitor, the Mac outputs separate HSYNC and VSYNC signals exactly like VGA requires, but at the mostly-useless portrait resolution of 640 x 870. For the 13 inch RGB monitor standard that we’re interested in, with 640 x 480 resolution, HSYNC and VSYNC are stuck high and the sync information is provided via CSYNC.

What about sync on green? Although it’s not mentioned anywhere in the developer note, the Mac also outputs sync on green any time it outputs composite sync. It outputs both CSYNC and sync on green. In fact, it also outputs sync on red and sync on blue too – all three color channels have embedded sync information when composite sync is used. This was recently proven conclusively with a video hardware schematic analysis followed by a series of tests by dougg3 (Doug Brown), who kindly gave me permission to reproduce his oscilloscope captures here.

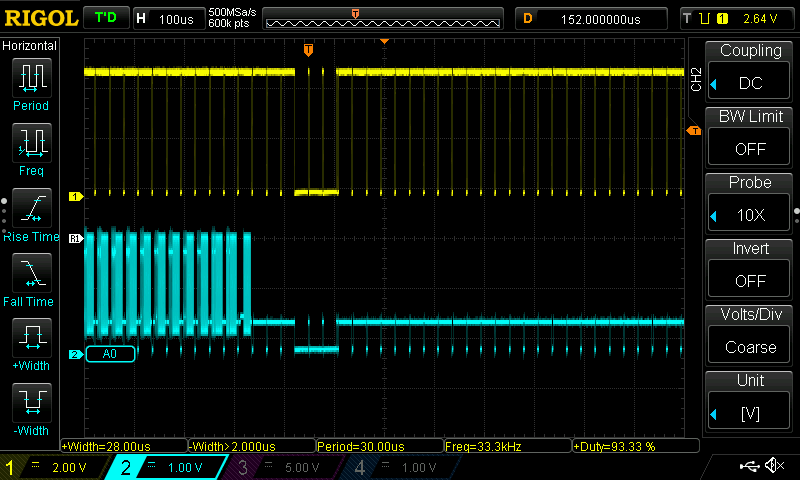

Doug hotwired his IIci’s monitor connector, grounding pin 4 (sense 0) to produce the monitor ID for 640 x 480 RGB. He made this scope capture showing the Mac’s CSYNC output (yellow trace) and red video signal (cyan trace). On CSYNC you can see the shorter HSYNC pulses and the longer VSYNC pulse combined with the HSYNC pulses during it. On the red channel, you can see some red video data on the left, with the sync info clearly also present in the lower voltage range.

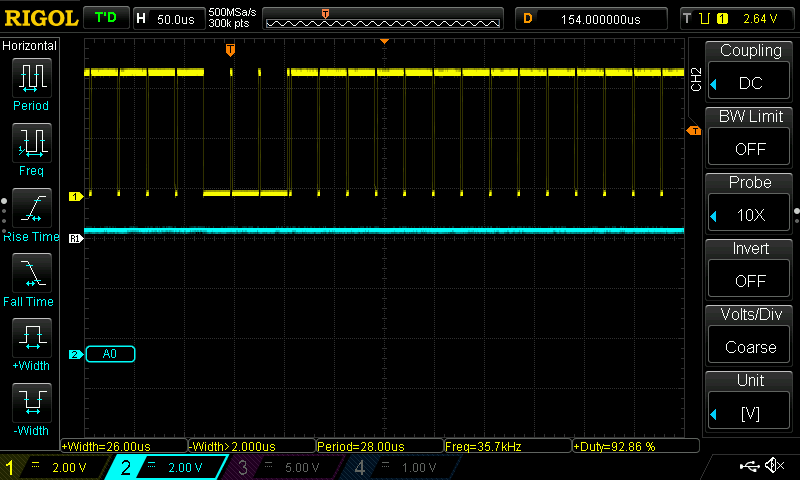

Looking at the green channel also showed the same thing – embedded composite sync in the green video data. Doug then looked at the VSYNC output (cyan trace):

Nothing. VSYNC was just a constant high voltage. Nothing to see here. This confirms the information from the developer note: when CSYNC is output, VSYNC and HSYNC are turned off.

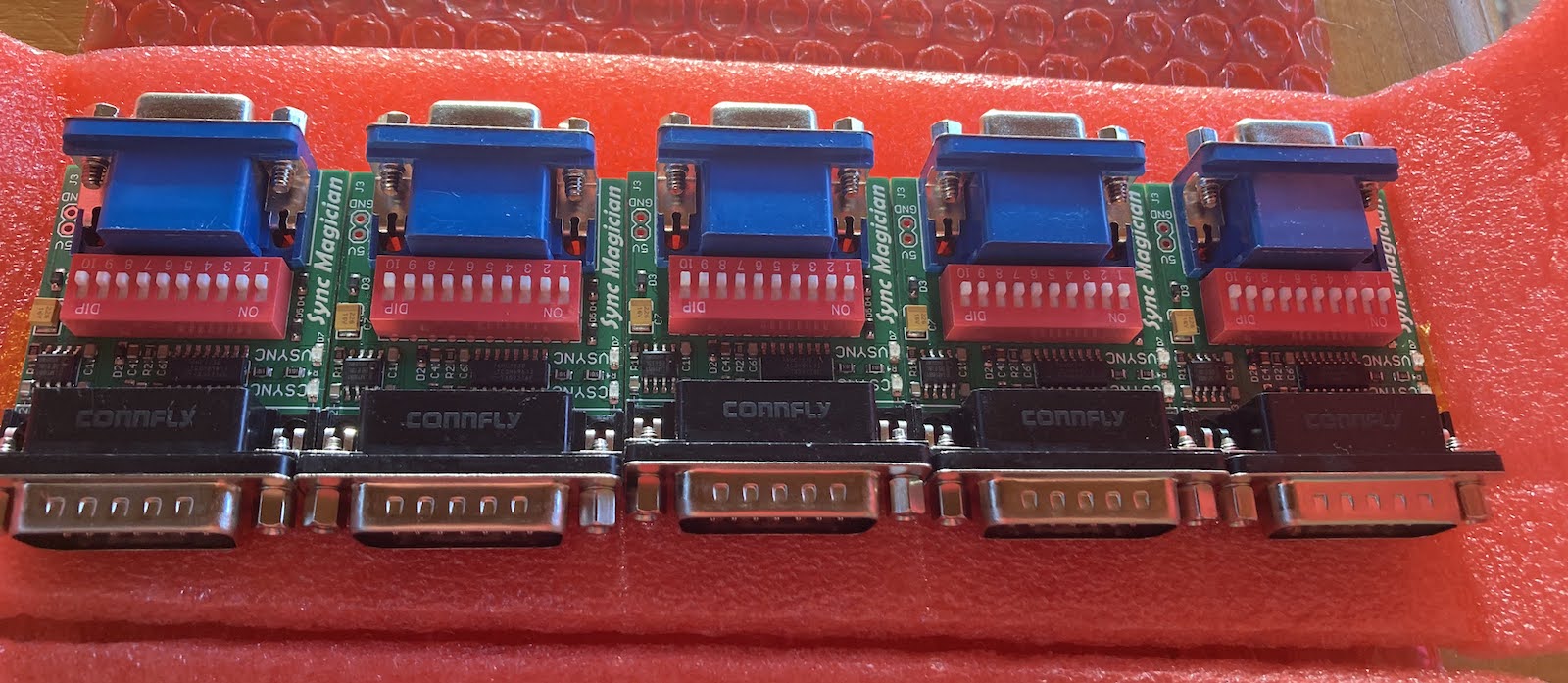

DIP Switch VGA Adapters

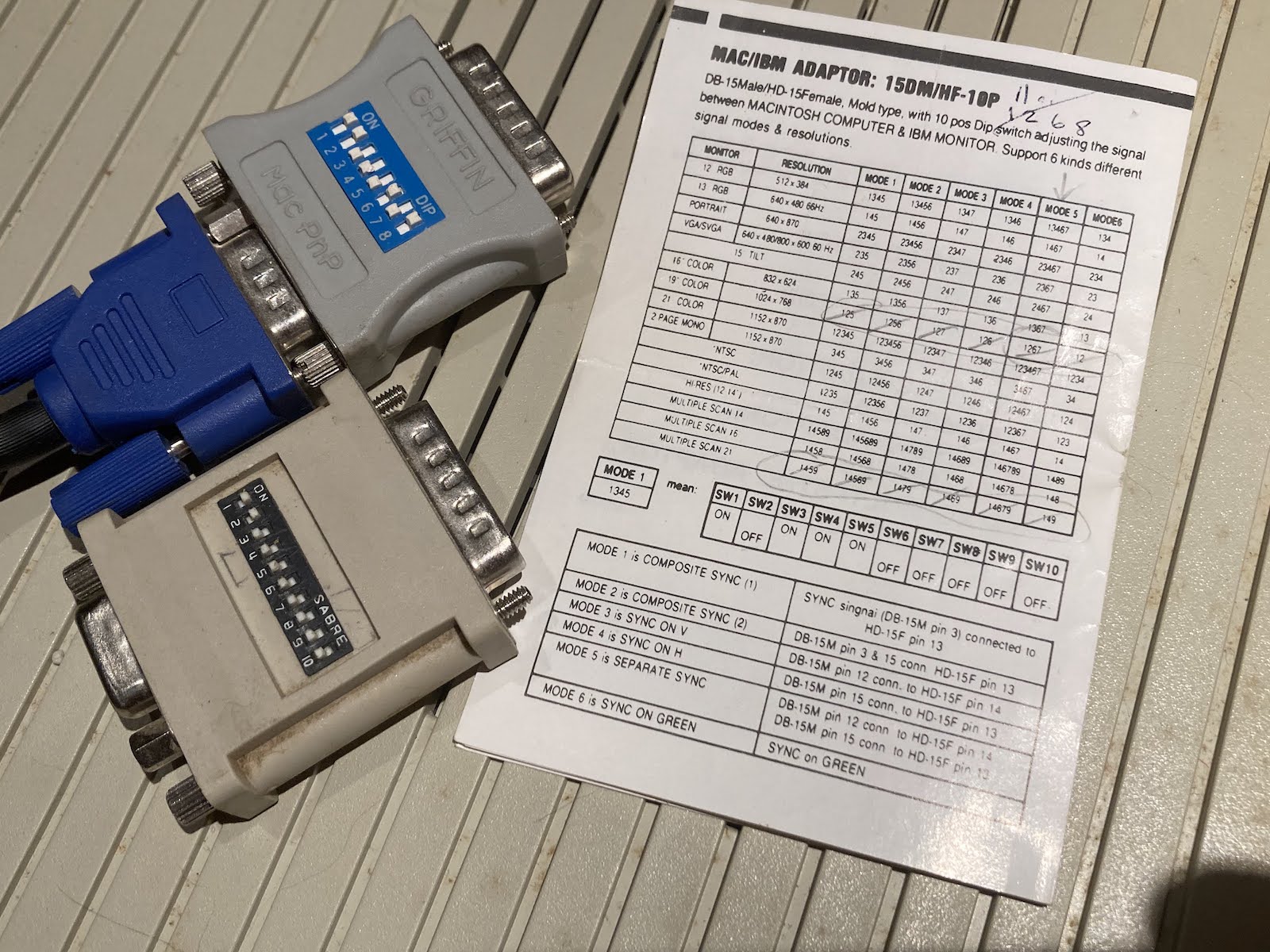

Now we know enough to begin peeking inside the common Mac to VGA adapters, with their confusing arrays of DIP switches, to understand how they work. If you’ve been around classic Macintosh computers for a while, you’ve surely seen many variations of these:

Obviously they are physical adapters from DB-15 to HD-15, but what do all those DIP switches do? For nearly all such adapters, the guts are simply a passive switch matrix, controlling how the Mac pins are connected to the VGA pins. There’s no signal processing of any kind. The DIP switches typically perform two functions:

Monitor ID – Configure how the sense pins are connected to ground, or to each other, to set the desired monitor ID. This tells the Mac what kind of video signal to generate.

Sync mapping – VGA VSYNC can optionally be connected to Mac VSYNC. VGA HSYNC can be connected to Mac HSYNC or Mac CSYNC.

They’re pretty simple devices. Maybe you’re wondering why you’d ever want to connect the Mac’s CSYNC to the VGA monitor’s HSYNC. Many newer monitors are able to accept composite sync as an alternative to HSYNC and VSYNC, and if they have that capability, they will normally expect CSYNC on their HSYNC input. Providing a DIP switch mapping for this will enable the Mac to work directly with such monitors.

Note that there are no DIP switch settings related to sync on green. If the monitor supports sync on green, it will use the sync info in the green video channel with no extra configuration needed. If the monitor doesn’t support sync on green, too bad.

The Sad Tale of One Macintosh IIci, Four Monitors, and No Joy

Are you still awake? With all of this background exposition finished, we’re finally ready to tell the story that inspired this whole investigation. It’s the story of my Macintosh IIci, four different monitors, a host of different Mac-to-VGA adapters, and a lot of frustration leading to eventual understanding and the design of a new video adapter.

For several years I’ve been using my Macintosh IIci with the Griffin Mac PnP adapter pictured above and a Dell 2001FP LCD monitor, and it’s worked great. This particular monitor also has a composite video input that works with Apple II and other classic computer hardware, so it’s an excellent tool for computer collectors. As to exactly how the Mac IIci video worked with this monitor, I never gave it any thought. I just plugged it in and got a picture.

A couple of weeks ago I went on a shopping spree and purchased a ViewSonic VG900b 19-inch LCD, a Viewsonic 6 TX-14H30 14-inch CRT, and an E-Machines ColorPage T16 II 1108DT16MR 16-inch CRT. These are all multisync displays, with a max resolution of 1024 x 768 on the CRTs and 1280 x 1024 on the LCD. But when I connected them to my Mac IIci with the Griffin adapter, I got no picture from any of them. I tried zillions of DIP switch settings, I tried different adapters, but nothing helped. All three of these fussy monitors simply refused to show any image from my IIci. They behaved as if nothing were connected.

Now that we understand the video signals and the inner workings of the DIP switch adapters, we can see the likely reason that nothing worked. In 640 x 480 mode the Mac IIci outputs composite sync and sync on green. My 2001FP must support one or both of those sync standards, but the new monitors probably don’t support them. In the case of the VG900b this was confirmed in the hardware specifications listed in its manual, where it lists support for “H/V Separated (TTL)” video sync. Other Viewsonic LCDs from the same era specifically mention composite sync and sync on green in their specifications, so this isn’t likely just an accidental omission from the documentation. I haven’t been able to find detailed specifications for the two CRT monitors, but I’m guessing it’s the same issue. These monitors require separate HSYNC and VSYNC signals, and won’t support any other sync format.

LM1881 to the Rescue

What do you do when your computer outputs composite sync, but your monitor requires separate HSYNC and VSYNC? Say hello to the Texas Instruments LM1881 Video Sync Separator.

This chip is designed to extract composite sync from composite video, a video standard in which composite sync is mixed with RGB color data. In our case the composite sync is already separated from the color data and doesn’t need to be extracted, but the LM1881 has another feature we can take advantage of: synthesis of a separate VSYNC signal from the composite sync input. Unfortunately the LM1881 doesn’t have a complementary HSYNC output. There are other rarer and more expensive chips that can extract both HSYNC and VSYNC, but I haven’t investigated these.

Fortunately for us, I’ve learned that many (most?) monitors will accept CSYNC as a substitute for HSYNC, so long as a separate VSYNC signal is also provided. So all we really need is VSYNC, and the LM1881 can do the job.

Armed with this information, I set out to build a Mac to VGA adapter with an integrated LM1881 that would enable my Macintosh IIci to work on those three fussy monitors. I would use the LM1881 to extract VSYNC from CSYNC, passing the VSYNC to the VGA monitor, and I would pass CSYNC to HSYNC with my fingers crossed.

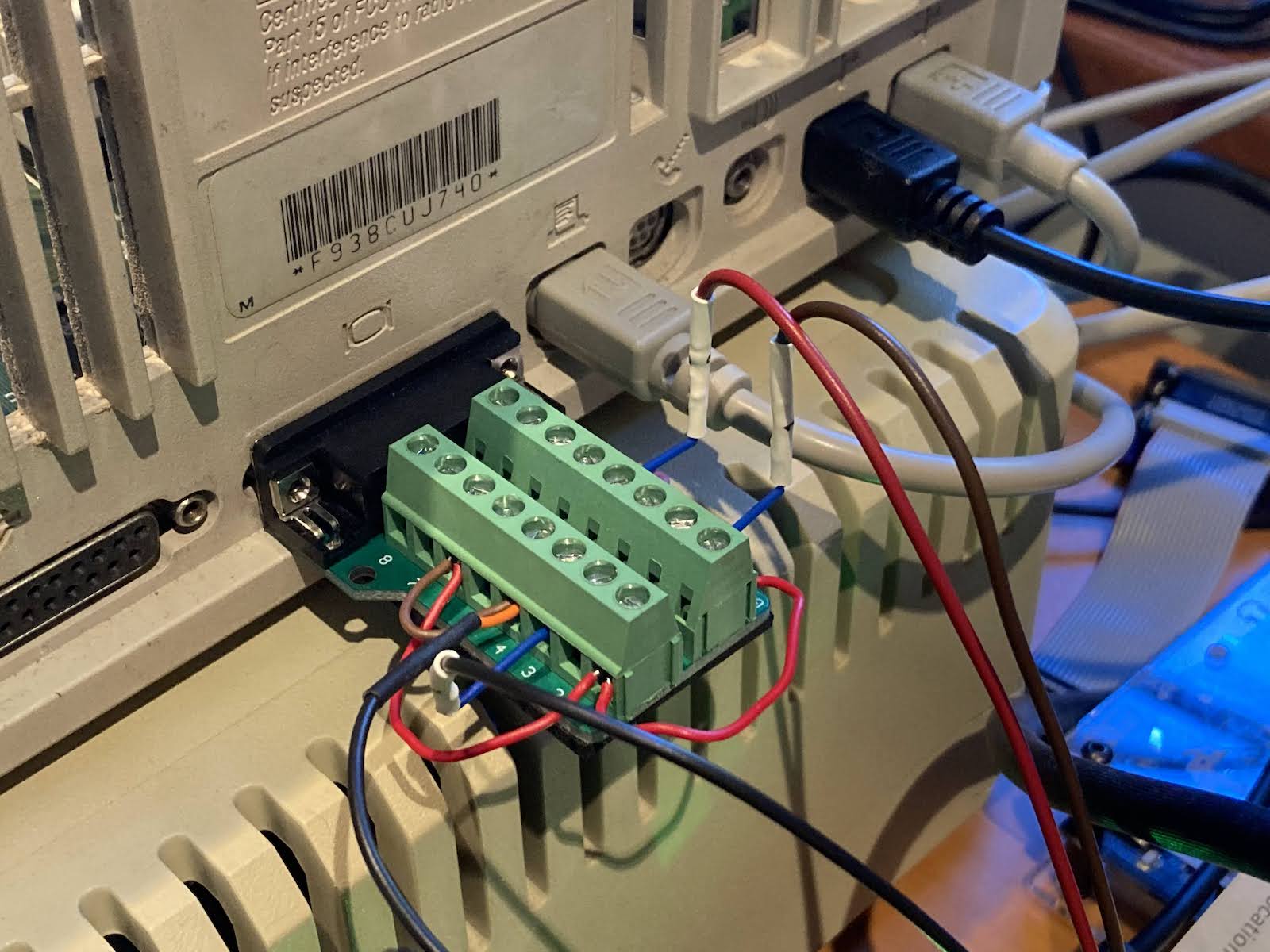

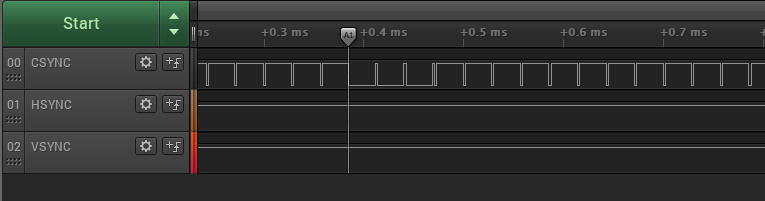

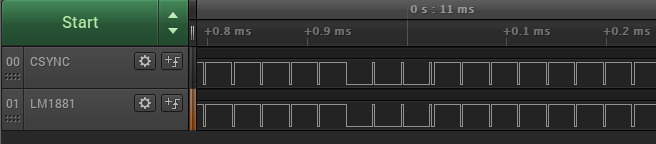

I began with a DB-15 breakout. I connected up all the grounds, and grounded pin 4 (sense 0) to request Mac 13 inch 640 x 480 mode. I plugged the breakout into my Macintosh IIci, and connected a logic analyzer to all three sync outputs. CSYNC showed the expected composite sync with a period of 15 ms (66.67 Hz), while HSYNC and VSYNC remained high.

Next I soldered some wires to an LM1881 breakout PCB. The LM1881 requires a 5V supply, which isn’t present on the monitor connector, so I stole 5V from the floppy disk port. Later I intend to try self-powering the LM1881 using the (otherwise unused) VSYNC and HSYNC signals as a power source.

Examining the LM1881 composite sync output, I saw that the output followed the input as expected.

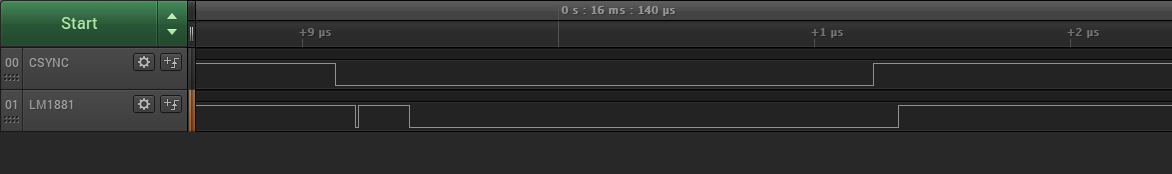

But zooming in, the signals were not quite the same. The LM1881 output lagged the CSYNC input by about 100ns, and included a very short low pulse before going high and low again, for each pulse on the CSYNC input. This might have been an artifact of using a logic analyzer to view the signal, rather than an analog oscilloscope.

Then I soldered another wire to LM1881 pin 3, the synthesized VSYNC output. It worked! But the extracted VSYNC lagged the input VSYNC by a whole line, and extended several lines past the end of the input VSYNC. This was unexpected, but I believe the exact timing and duration of the VSYNC signal isn’t critical, so long as the refresh frequency is correct.

So far, so good. I finished the adapter by adding an HD-15 breakout. I connected the LM1881’s VSYNC output to VGA VSYNC, and LM1881 CSYNC output to VGA HSYNC. Remember, this second connection isn’t really correct – CSYNC is not HSYNC – but we’re relying on the premise that monitors will accept CSYNC on their HSYNC input as long as they also have a separate VSYNC signal. Thanks to the LM1881, we now had that missing VSYNC signal.

Here’s the finished adapter, including the floppy port adapter for stealing 5V: it really is a big mess o’ wires, and something so ugly that only a mother could love it.

I’ve mentioned that I have one monitor that’s worked with my IIci’s built-in video all along: the Dell 2001FP. And three monitors that do not work, no matter what settings I have tried on the VGA adapters: the Viewsonic VG900b LCD, Viewsonic 6 CRT, and E-Machines CRT.

As a sanity check, I tried the Dell first:

It still worked, but the video quality was lousy: there was all kinds of shimmering and noise in the image. Maybe it was a result of my messy nest of wires snaking everywhere? At least there was a usable image.

Next I tried the Viewsonic VG900b LCD. This was the real test, since this monitor had refused to sync with my IIci video before. Would it work now?

Whomp whomp, so sorry. There was no love from the VG900b, which still complained there was no video signal and then went to sleep. That was disappointing. Maybe the VG900b doesn’t like CSYNC as HSYNC substitute, or maybe it’s confused by the CSYNC that’s also still present on the RGB channels.

OK, how about this Viewsonic 6 CRT? It never worked with the IIci video before, but how about now?

Success, it worked! The image quality was pretty good too. There was still a little bit of shimmer, but much less than with the Dell 2001FP. I’m not sure why there was such a difference, maybe something about digital versus analog video circuitry?

The final test was the E-Machines 16 inch CRT. This was the third member of the fussy trio that had refused to work with my IIci built-in video before:

Huzzah! It also worked (minus some image centering). The image quality was similar to the Viewsonic CRT: some shimmer, but not too bad.

Design of a New Mac-to-VGA Adapter

That’s a score of 2 out of 3 for this Mac-LM1881 adapter. I think that’s useful enough to deserve being made into a proper PCB kit, for other classic Macintosh computer owners who’ve faced the same monitor challenges. Since it’s such a simple circuit, I’ll probably share the whole PCB design for anybody who wants to make their own, and also stock a few in the BMOW store for anybody that wants a pre-built adapater.

To assist with troubleshooting, I’d also like to include some LEDs in the adapter to show which of the Mac sync outputs have activity, and maybe also which of the RGB outputs have activity. I haven’t quite figured out how to do this. The RGB outputs are only 0.7V, and may have negative voltage swings if sync on green is used. The sync outputs are standard TTL levels with 0 to 5V swing. I’ve been brainstorming how to build an “activity detector” circuit to turn on an LED without involving a microcontroller. Maybe something with a flip-flop where the sync signal is used as the clock input, and there’s an RC circuit with appropriate time constant connected to the flip-flop’s asynchronous clear. If you have any great ideas for this, please share them.

Some questions about the LM1881 remain. I belatedly read the chip’s data sheet only after I’d finished my experimentation, and realized that I may be using it incorrectly, and that many of the similar circuits seen on the web are using it incorrectly. Referring to the canonical LM1881 circuit diagram shown above:

- Why didn’t the Viewsonic VG900b work with the LM1881 sync signals? Is there something simple I could do to fix it?

- The datasheet says the recommended input voltage on pin 2 is 1.5V and the absolute max is 3V, but I’m feeding it a 5V sync signal from the Mac.

- A different RC filtering scheme on input pin 2 may be needed – the 0.1 uF blocking capacitor is just an example. “Typical Applications” in the datasheet shows an alternative design with an RC lowpass filter on pin 2.

- The value of the R-set resistor may need to be adjusted, depending on video timing. The default value of 680 kOhm may be inappropriate for this.

- The LM1881 output pins can only source a few mA of current, but if I’m putting 5V into a 75 ohm terminated monitor input, won’t that be 67 mA? Do I need to buffer these signals? 67 mA is a pretty large amount of current, and more than even most buffers can provide. Perhaps I’ve misunderstood this. Do I also need a 75 ohm resistor at the source? Does 75 ohm termination even apply to the sync signals, or is that only for the RGB signals?

The investigation continues. More updates soon, I hope!

Read 19 comments and join the conversation